A Intel detalhou as características do 18A-P, versão aprimorada do nó de fabricação 18A que estreia nos processadores Panther Lake.

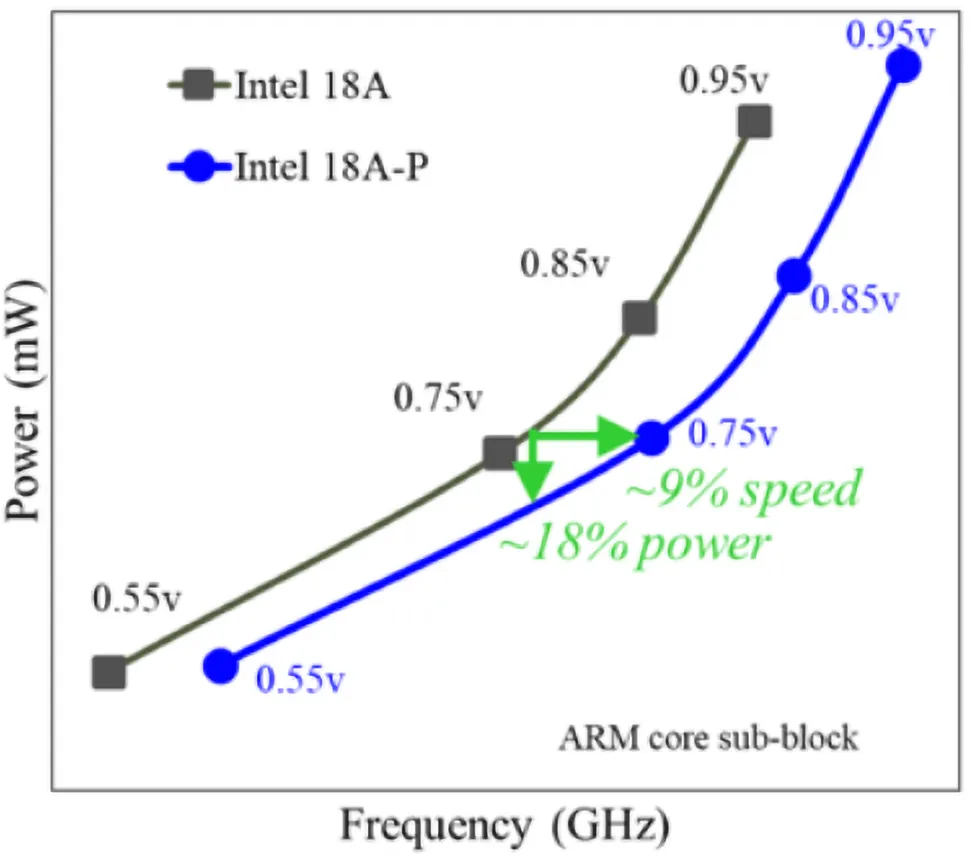

O paper liberado para o simpósio VLSI 2026, marcado para junho em Honolulu, indica 9% mais performance no mesmo consumo de energia ou 18% menos consumo na mesma performance. A condutividade térmica também sobe 50% em relação ao nó base.

A divulgação acontece pouco antes do evento e antecipa os ganhos da litografia destinada a clientes externos da Intel Foundry. A Apple aparece como uma das possíveis interessadas em usar o 18A-P para fabricar chips da família M-series para Macs e iPads, segundo rumores da indústria.

Os números colocam o 18A-P em um patamar próximo ao que se esperaria de uma transição completa de geração, como o salto de 18A para o futuro 14A. A diferença é que essa melhoria chega sem aumento de densidade de transistores, característica que costuma marcar uma nova litografia.

9% de performance ou 18% menos consumo

A comparação foi feita usando um sub-bloco padrão de núcleo ARM, em 0,75 V. O ganho de desempenho aparece quando os dois nós operam no mesmo consumo. A redução de consumo é registrada quando ambos rodam na mesma performance.

A Intel apresentou os números a partir de medições em frequência de Ring Oscillator, com teste de capacitância normalizada.

Em ambas as métricas, o 18A-P exibe melhoria sobre o 18A, principalmente em bibliotecas de 180 CH (compatíveis com altura padrão de células lógicas).

Em pontos de tensão mais alta (0,85 V e 0,95 V), o gráfico mostra que o 18A-P sustenta as vantagens, com a curva de potência ficando consistentemente abaixo da curva do 18A para a mesma frequência.

Novos tipos de transistor RibbonFET

O 18A-P amplia o catálogo de transistores RibbonFET com gate-all-around (GAA) e backside power delivery via PowerVia. A litografia introduz dois novos tipos de dispositivos: um de alta performance com contatos aprimorados (Z3P) e novos de baixo consumo (Z1 e Z1.5).

A diversificação permite ao designer escolher transistores mais rápidos para os caminhos críticos do projeto e dispositivos mais econômicos para regiões menos exigentes. Em chips complexos, o resultado costuma aparecer como melhor balanço geral entre desempenho e eficiência.

A Intel também adicionou mais opções de tensão de threshold (VT). O 18A trazia 4 pares de logic VTs. O 18A-P sobe para mais de 5 pares, com uma nova classe entre ULVT e LVT, além de um ULVT mais baixo. O ganho é de granularidade fina no binning dos chips finais.

Condutividade térmica 50% maior

O ganho térmico tem aplicação tanto em chips para clientes finais quanto em CPUs de Data Center. A redução da resistência térmica ajuda a controlar a alta densidade de potência típica dos transistores GAA, que concentram o calor em áreas menores.

A própria Intel descreve o nó na página oficial do VLSI 2026:

18A-P entrega mais de 18% menos consumo a iso-performance ou 9% a iso-power.

Na frente da estabilidade de longo prazo, o 18A-P melhora o NBTI (negative-bias temperature instability) lógico, aumentando a vida útil em condições de tensão alta.

O ajuste é considerado decisivo para CPUs de servidor que operam em alta carga por anos consecutivos. O nó também alinha melhor a tensão mínima de operação (Vmin) entre lógica e SRAM.

Aperto de 30% nos skew corners eleva o rendimento

Outro ponto técnico do paper é o skew corner tightening de 30%. A medida reduz a variação entre silício rápido e silício lento dentro de uma mesma wafer e entre o centro e a borda de cada lâmina.

Na prática, mais dies saem da fábrica dentro das especificações desejadas, o que aumenta o rendimento paramétrico. Para a Intel Foundry, o ganho é financeiro: mais chips de alta qualidade por wafer significa mais margem em cada lote produzido.

A litografia mantém a densidade de defeitos similar ao 18A, ou seja, problemas com line-edge roughness (LER) e variabilidade estocástica não foram resolvidos nessa transição. O ataque é à dispersão paramétrica, não aos defeitos de fabricação propriamente ditos.

Compatibilidade total com o 18A

O 18A-P preserva o contacted poly pitch de 50 nm e as alturas de library de 180 e 160 nm. O resultado é compatibilidade direta de design: um chip projetado para o 18A pode ser portado para o 18A-P sem reescrita do layout.

Os ganhos de processo aplicam-se ao silício automaticamente, mas para extrair o desempenho máximo das novas estruturas de transistor é preciso reotimizar o projeto. Esse modelo de migração reduz custo e tempo para clientes que já estavam projetando para o 18A original.

A Intel também afinou a resistência e a capacitância das primeiras camadas de metal (V0 a V2 e M2 a M4). A empresa não detalhou os números absolutos, mas a mudança influencia diretamente velocidade de sinal, consumo e timing dos circuitos.

A tabela abaixo resume as diferenças entre os dois nós:

| Característica | 18A | 18A-P |

|---|---|---|

| Performance @ Iso-Power | 1x (referência) | +9% |

| Contacted Poly Pitch | 50 nm | 50 nm |

| Library Height | 180 nm e 160 nm | 180 nm e 160 nm |

| Pares de Logic VT | 4 | 5+ (com nova VT entre ULVT e LVT) |

| Skew Corners | base | aperto de ~30% |

| Interconnect RC | base | redução em V0-V2, jogs em M2-M4 |

| Condutividade Térmica | base | +50% |

| Transistor LP | Z1, Z2, Z3 | Z1 (LP), Z1.5 (LP), Z2, Z3 |

| Transistor HP | Z2, Z3 | Z3P (HP contact) |

Apple e outras fabless de olho no 18A-P

A versão mais madura do 18A é justamente a que tem chamado a atenção de clientes externos. A Intel chegou a considerar manter o 18A como nó interno apenas, mas mudou de postura quando empresas fabless começaram a sinalizar interesse no 18A-P.

A Apple aparece com mais força nos rumores, com a possibilidade de fabricar chips M-series para MacBooks e iPads no nó da Intel. A escolha faria sentido também por motivos geopolíticos, com pressão dos Estados Unidos sobre a dependência da TSMC em Taiwan.

O movimento marca uma virada para a Intel Foundry. Lip-Bu Tan, atual CEO da empresa, manifestou ceticismo no início do mandato sobre a viabilidade do nó como produto comercial para terceiros.

O 18A-P está mudando essa avaliação dentro da própria companhia.

Leia também:

- Intel, AMD e MediaTek aumentam produção, mas preços de CPUs seguem em alta

- Intel transforma CPUs “sucata” em vendas e aumenta produção em meio à escassez

- INTEL WILDCAT LAKE explicados! Direto do IEM 2026

VLSI 2026 marca a estreia oficial do 18A-P

A Intel deve apresentar o paper completo no VLSI 2026, em Honolulu, no Havaí, em junho. O simpósio é a principal vitrine acadêmica da indústria de semicondutores e ocorre próximo ao período em que a TSMC também detalha sua resposta direta, o nó A16.

A linha de produção do 18A já está em operação para Panther Lake, e a empresa sinalizou que o ramp do 18A-P chega “nos próximos trimestres”. Sem data oficial firme, mas com calendário apertado para alinhar com a janela de produtos da Apple e de outras fabless interessadas.

Os números prometidos sustentam um caso forte para reverter a perda de market share recente da Intel. R$ 7,87 bilhões em corte de custos, demissões e a entrada de Lip-Bu Tan no comando deixaram a empresa em modo de reorganização.

A expansão da carteira de clientes externos é a próxima etapa dessa estratégia, e o 18A-P é a peça central dela.

Fonte(s): VLSI 2026 Symposium