Pesquisadores do imec e da Universidade de Ghent anunciaram um resultado inédito: conseguiram crescer 120 camadas alternadas de Silício (Si) e Silício-Germânio (SiGe) em um wafer de 300 mm. O feito coloca a indústria mais perto da chamada memória DRAM tridimensional (3D DRAM), uma tecnologia que pode aumentar a densidade de dados sem ampliar a área dos chips.

Em termos práticos, é como construir um arranha-céu em escala nanométrica, onde cada andar representa uma camada da memória. O desafio é que, ao contrário de concreto e aço, os materiais tendem a se expandir e se contrair de maneiras diferentes, criando tensões que podem levar ao colapso de toda a estrutura.

Por que 120 camadas representam um desafio tão grande

Em semicondutores, cada camada depositada precisa manter coesão cristalina com a anterior, ou seja, os átomos devem se alinhar quase perfeitamente.

O problema é que o Silício e o Silício-Germânio têm constantes de rede diferentes: enquanto os átomos de silício ficam mais “próximos”, os de SiGe ocupam um espaço maior. O descompasso, chamado lattice mismatch, gera tensões internas que se acumulam a cada nova camada.

Com poucas camadas, é possível “acomodar” essa diferença sem grandes impactos. Mas quando se chega a dezenas ou centenas de repetições, a probabilidade de formação de defeitos cresce exponencialmente. Assim, esses defeitos, conhecidos como dislocações e falhas de empilhamento, interrompem a continuidade elétrica e podem inutilizar a memória.

Vale ressaltar que é necessário manter uniformidade absoluta na espessura, que chega à escala de nanômetros. Se uma camada for alguns angstrons mais grossa ou mais fina que o previsto, essa variação pode ser multiplicada em todas as camadas seguintes, comprometendo a estabilidade estrutural. É como tentar construir um prédio onde cada andar tem altura ligeiramente diferente: ao final, o edifício se inclina.

Por isso, chegar a 120 camadas bem alinhadas e sem colapsos mostra que os cientistas conseguiram não apenas controlar a composição dos materiais, mas também dominar a física de tensões atômicas, algo que até então limitava o avanço do empilhamento vertical em memórias.

A dificuldade de empilhar materiais distintos

O obstáculo central é o descasamento de rede cristalina. Enquanto o silício tem um espaçamento atômico fixo, o Silício-Germânio ocupa um espaço ligeiramente maior.

Ao empilhar dezenas de camadas, as diferenças se acumulam e podem gerar defeitos chamados dislocações de rede, que comprometem a condutividade e reduzem o rendimento dos chips.

Para contornar o problema, os cientistas ajustaram cuidadosamente a porcentagem de Germânio no SiGe e testaram a adição de carbono, que atua como um “amortecedor” capaz de aliviar parte do estresse.

Além disso, foi necessário manter um controle de temperatura extremamente uniforme durante o processo de deposição, já que mínimas variações podem deformar toda a pilha.

Deposição epitaxial: pintando com gases

O método usado é chamado de deposição epitaxial, no qual gases como silano (SiH₄) e germano (GeH₄) são decompostos na superfície do wafer.

Cada camada depositada tem apenas alguns nanômetros de espessura, e o controle sobre espessura, composição e uniformidade deve ser absoluto. Um pequeno erro no início pode se multiplicar até a última camada.

Estamos literalmente criando estruturas que a natureza por si só não construiria. Ao dominar a tensão atômica, conseguimos erguer uma pilha de 120 camadas que pode servir de base para memórias de altíssima densidade

Pesquisadores envolvidos no estudo

Por que isso importa para a indústria

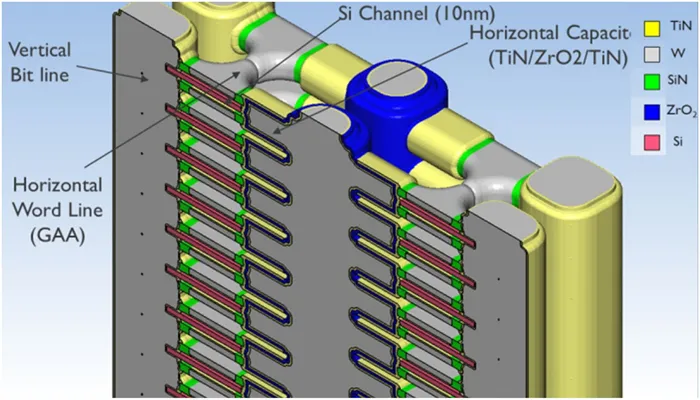

A arquitetura atual da DRAM é bidimensional, limitando a quantidade de células de memória que cabem em uma mesma área.

O empilhamento vertical rompe essa barreira e abre espaço para chips mais compactos e com maior capacidade, sem exigir aumentos de tamanho físico ou consumo desproporcional de energia.

Além do impacto direto em DRAM, a técnica pode ser aproveitada em transistores de nova geração, como GAAFETs e CFETs, que dependem de precisão absoluta no crescimento de camadas.

A técnica também pode influenciar projetos de lógica empilhada e até arquiteturas de computação quântica, onde cada átomo conta.

Leia também:

- Novo chip de luz de 100 GHz supera todos os limites atuais da tecnologia

- Cientistas criam primeiro chip cerebral de micro-ondas que pensa como IA e se comunica via rádio

- Pesquisa sobre chips da China supera muito os EUA em volume de artigos e número de citações

Um excelente perspectiva na corrida pelo 3D

Empresas como a Samsung já possuem planos explícitos para DRAM tridimensional e contam com centros de P&D dedicados a esse objetivo.

O experimento de 120 camadas mostra que o conceito está saindo do papel e se tornando uma possibilidade concreta para a próxima década de chips de memória.

O resultado não representa ainda um produto final, mas um marco experimental que dá confiança para que a indústria avance em direção a dispositivos reais. Se consolidada, a técnica pode redefinir os limites de armazenamento e eficiência, preparando terreno para uma nova fase da microeletrônica.

Fonte: AIP Publishing